Burst Error Ratio Tester

rBT2250

25G Burst Mode Bit Error Ratio Tester

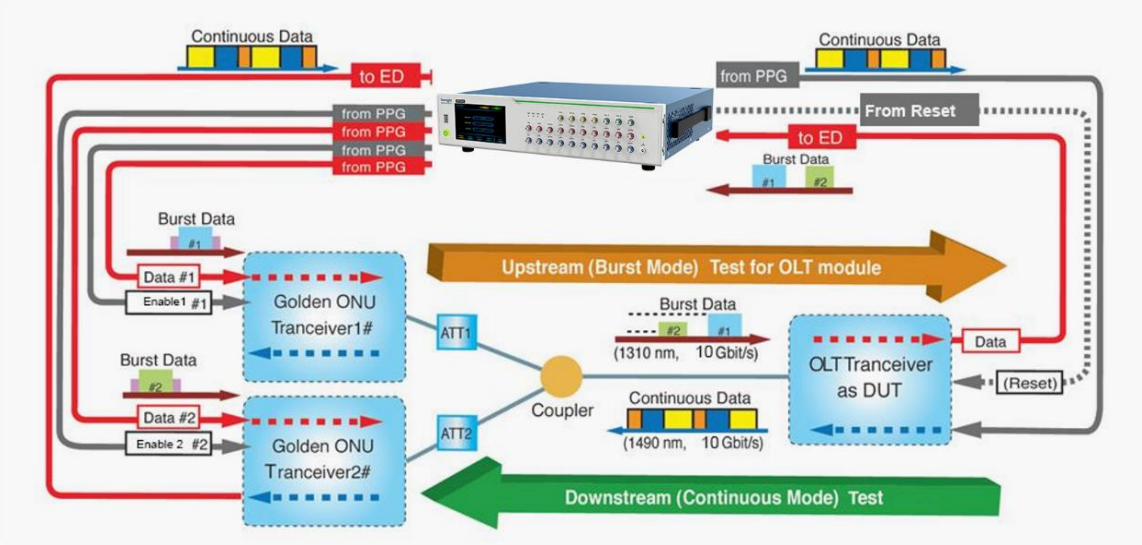

rBT2250 is a Burst Mode Bit Error Ratio Tester to evaluate 10G/25G/50G OLT (Optical Line Terminal) receiver performance in burst mode. rBT2250 provides 2 independent pattern generator/error detector channels, and provide laser enable/ receiver reset /RSSI trigger signals and SD signal detect function. With built-in burst clock data recovery, clock would be recovered from the burst data every time, it is a must in long fiber testing. The high integration multi-channel design of rBT2250 make it the best choice for burst bit error ratio analysis.

Features

Multi-rate

Burst Rate:9.953/ 10.3125/12.4416/

Support Combo-PON test

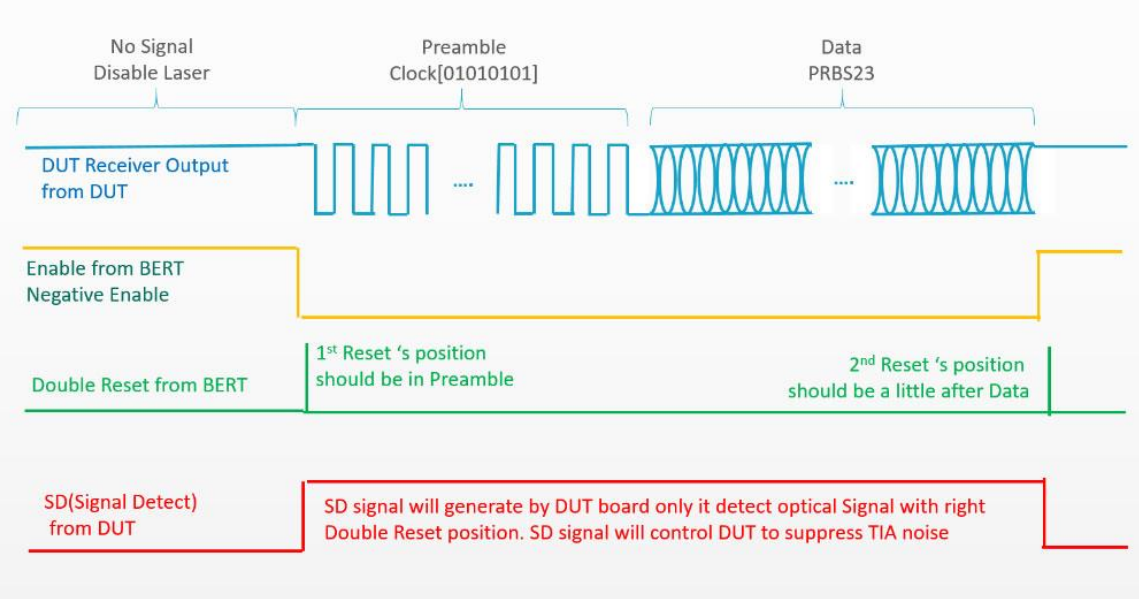

Dual reset signal, support Combo-PON test

SD Test

Individual LOS monitoring/SD monitoring/LOS judgment for each channel

Built-in clock recovery

It can work in a real long-fiber environment, avoiding the influence of long-fiber on delay and jitterFeatures and Benefits

Double packet test

Each data packet has different attenuation, there are transitions between the phases of different data packets, and there are long consecutive "1" and "0" in the data packet.

Built-in clock recovery, support long fiber test

The built-in clock recovery enables the rBT2250 to work in a real long-fiber working environment, which is basically impossible in other solutions commonly used in the industry, because those systems do not support clock recovery and cannot adapt to the effects of long-fiber on delay and jitter.| Pattern Generator Specifications | Output | Differential |

AC coupling, 100 Ω Termination |

| Single End | AC coupling, 50 Ω termination | ||

| Output Amplitude 300-600 mVp-p | Differential |

||

| Output Channel |

2 in-depended Burst Channels | Burst/Continuous mode |

|

1 Continuous Channel |

Continuous mode | ||

| Pattern | PRBS7,23,31,User Defined,CID pattern | ||

| Support data rate | 9.953/10.3125/12.4416/24.8832/25.78125 Gbps | ||

| Rise Time | <20 ps | 20%~80% | |

| Jitter | <1 ps | RMS | |

| Pre-emphasis | Support Pre-Cursor & Post Cursor adjustment to minimize testing fixture or RF cable insertion loss |

||

| Pattern Sequence | Each Channel can be set preamble/payload/guard-time pattern sequence in-dependently |

||

| CID code type | Support add continuous “1”,continuous “0” pattern as length from 64-128 bits (adjustable) |

||

| connector type | 2.92 mm female, 50 Ω |

||

| Clock/ Trigger and control channel | Trigger output | Support Frame Trigger output |

|

| Clock Output | 1/2、1/4、1/8、1/16 divided clock output |

||

| Laser Enable Channel | Support 2 laser enable control channel outputs( each enable control channel is synchronized with Pattern Generator channel) |

||

| Enable Output Level | TTL level, support high/low enable and continuous High/Low | ||

Reset Channel |

Support 2 reset channel outputs (reset channel is synchronized with error detector channel) |

||

| Reset Width | Adjustable |

||

| Reset Position | Adjustable, support Auto-Range to find the right reset position |

||

| RSSI Trigger out | Support RSSI trigger (adjustable for RSSI trigger pulse width/repeat frequency and position) |

||

| Bit Error Detector Specifications | Input type | Differential/Single end |

|

| Data Rate | 9.953/10.3125/12.4416/24.8832/25.78125 Gbps | ||

| Impedance | 100 Ω | ||

Input Amplitude Range |

100~800 mVp-p | ||

| Sensitivity | >100 mV | ||

| Clock Mode | Internal burst clock data recovery unit |

||

| Synchronize | Auto-synchronization and Auto-range |

||

| Connector | 2.92 mm female, 50 Ω | ||

文档下载

rBT1250 X-PON突发信号误码测试仪-使用说明书

rBT1250 X-PON突发信号误码测试仪-使用说明书Similar recommendation

Service hotline

Follow

Name

Email verfication code

Phone

Password

Confirm Password

e-mail address

Email verification code

New Password

Confirm Password